FPGA的機載合成孔徑雷達(dá)數(shù)字信號處理機接口板卡的

機載合成孔徑雷達(dá)(Synthetic Aperture Radar,簡稱SAR)是以“合成孔徑”原理和脈沖壓縮技術(shù)為理論基礎(chǔ),以高速數(shù)字處理和精確運動補償為前提條件的高分辨率成像雷達(dá)對于機載合成孔徑雷達(dá)成像處理來講,僅有目標(biāo)的原始回波數(shù)據(jù)是不夠的,還必須獲得雷達(dá)和載機的參數(shù)另外,為了滿足信號處理機實時處理的要求,要求輸入到處理機的各種數(shù)據(jù)符合處理機成像處理的數(shù)據(jù)格式這樣,處理機在獲得數(shù)據(jù)幀后就可以直接進(jìn)行成像處理而不必再有格式轉(zhuǎn)換的開銷但是 目標(biāo)的原始回波數(shù)據(jù)與雷達(dá)和載機的參數(shù)數(shù)據(jù)來自兩個不同的設(shè)備它們的數(shù)據(jù)格式和時序都是由各自的設(shè)備確定的,因此信號處理機便面臨著與外圍設(shè)備接口的問題

本文引用地址:http://cafeforensic.com/article/190521.htm1 系統(tǒng)功能

在本機載合成孔徑雷達(dá)系統(tǒng)中,進(jìn)出接口板卡的數(shù)據(jù)流包括數(shù)據(jù)采集設(shè)備輸入的原始回波數(shù)據(jù)監(jiān)控設(shè)備輸入的雷達(dá)和載機的參數(shù)數(shù)據(jù)以及輸出到處理機的成像處理數(shù)據(jù)它們有如下特點:①輸入數(shù)據(jù)流的速度和時序不匹配數(shù)據(jù)采集設(shè)備和監(jiān)控設(shè)備是兩個異步的系統(tǒng),它們都有自己的定時控制電路,以自己的速度傳輸數(shù)據(jù)②輸入輸出數(shù)據(jù)流的信息格式不匹配數(shù)據(jù)采集設(shè)備輸入的原始回波數(shù)據(jù)和監(jiān)控設(shè)備輸入的雷達(dá)和載機的參數(shù)數(shù)據(jù)采用FPDP協(xié)議傳輸,接口板卡輸出到處理機的數(shù)據(jù)采用Link口傳輸協(xié)議進(jìn)行傳輸

考慮到進(jìn)出接口板卡數(shù)據(jù)流的特點和雷達(dá)系統(tǒng)對接口板卡的控制要求,接口板卡要具有如下功能:

(1)設(shè)置數(shù)據(jù)的緩沖存儲邏輯,以適應(yīng)不同設(shè)備之間的速度差異和時序差異;

(2)進(jìn)行信息格式轉(zhuǎn)換,將目標(biāo)的原始回波數(shù)據(jù)與雷達(dá)和載機的參數(shù)數(shù)據(jù)打包,插入相應(yīng)的幀信息形成處理機要求的數(shù)據(jù)幀,并控制數(shù)據(jù)流的走向;

(3)實現(xiàn)PCI接口,能夠產(chǎn)生PCI中斷;

(4)具有在線自檢測功能

2 系統(tǒng)硬件結(jié)構(gòu)設(shè)計

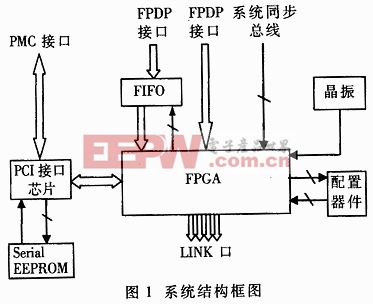

為了簡化系統(tǒng)硬件設(shè)計,增加系統(tǒng)的靈活性,采用FPGA芯片實現(xiàn)系統(tǒng)要求的數(shù)據(jù)格式轉(zhuǎn)換打包分發(fā)和邏輯控制功能數(shù)據(jù)緩存采用硬件FIFO和軟件雙口RAMPCI接口采用專用接口芯片實現(xiàn)硬件FIFO和軟件雙口RAM的寫時鐘分別由各自的FPDP接口提供,其它時鐘由接口板上的晶振提供系統(tǒng)的硬件結(jié)構(gòu)框圖如圖1所示

2.1 輸入數(shù)據(jù)流的緩存方案

為了適應(yīng)處理機與數(shù)據(jù)采集設(shè)備和監(jiān)控設(shè)備之間的速度差異,解決速度不匹配問題,需要將輸入的數(shù)據(jù)先進(jìn)行緩存數(shù)據(jù)采集設(shè)備送入的原始回波數(shù)據(jù)每幀的數(shù)據(jù)量比較大,接口板卡上設(shè)計了硬件FIFO作為原始回波數(shù)據(jù)的緩存器,FIFO的讀寫使能由FPGA編程控制,寫時鐘由FPDP接口提供,讀時鐘由接口板卡上的晶振提供數(shù)據(jù)采集設(shè)備和監(jiān)控設(shè)備是兩個異步的系統(tǒng),雷達(dá)參數(shù)數(shù)據(jù)流和原始回波數(shù)據(jù)流之間沒有同步關(guān)系,一幀雷達(dá)參數(shù)數(shù)據(jù)對應(yīng)幾幀原始回波數(shù)據(jù),因此設(shè)計中用雙口RAM作為雷達(dá)參數(shù)數(shù)據(jù)的緩存器另外,每幀雷達(dá)參數(shù)的數(shù)據(jù)量比較小,本設(shè)計在FPGA內(nèi)利用參數(shù)化的模塊庫(Library of Parameterized Modules,簡稱LPM)中的lpm_ram_dp編程實現(xiàn)雙口RAM,簡化了硬件設(shè)計

2.2 PCI接口設(shè)計

實現(xiàn)PCI接口的方案一般有兩種:采用可編程邏輯器件和采用專用總線接口器件采用可編程邏輯器件實現(xiàn)PCI接口的最大好處是比較靈活,缺點是設(shè)計難度較高,開發(fā)周期較長采用專用接口器件實現(xiàn)雖然沒有采用可編程邏輯器件實現(xiàn)那么靈活,但能夠有效地降低接口設(shè)計的難度,縮短開發(fā)時間本系統(tǒng)采用專用接口器件PCI9052實現(xiàn)接口板卡的PCI接口

接口板卡的硬件資源為映射到FPGA內(nèi)部寄存器的I/O映射空間和一個中斷源PCI9052提供5個局部地址空間,選用Space0作為接口板的地址空間,分配16個8位地址同時設(shè)置相應(yīng)的初始化,PCI配置寄存器中的PCIBAR2設(shè)置為0XFFFFFFF0,向系統(tǒng)請求分配內(nèi)存的數(shù)量為16設(shè)置局部地址空間的范圍為0X01000000~0X01000010PCI9052提供兩個局部中斷源,選用LINTi1FPGA提供電平觸發(fā)中斷信號,因此PCI9052的中斷觸發(fā)模式設(shè)置為電平觸發(fā)利用PCI9052的局部設(shè)備片選信號CS0#作為FPGA的片選信號CS0#片選信號的起始地址和地址范圍由CS0 Base Address寄存器的設(shè)置值0x01000011決定,即起始地址為1000000h,地址范圍為20hPCI9052寄存器的初始值由串行EEPROM提供,在PCI9052加電后讀取EEPROM必須采用支持連讀功能的芯片,本設(shè)計中采用FairChild Semiconductor公司的93CS46N

2.3 FPGA的配置設(shè)計

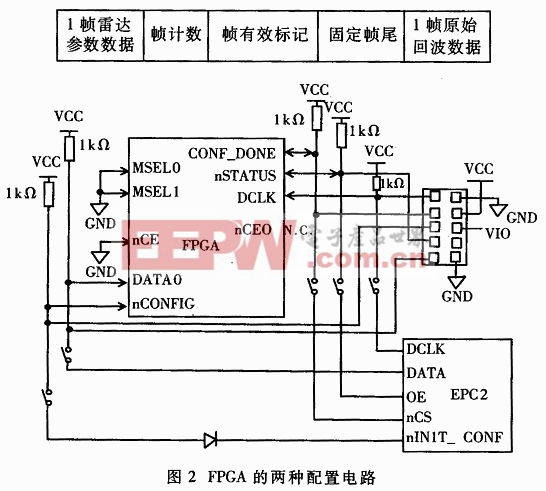

本設(shè)計為FPGA提供了兩種配置方式:主動串行配置和被動串行配置

主動串行配置由EPC2向FPGA器件輸入串行位流的配置數(shù)據(jù)在該配置方式下,一直由FPGA控制著配置過程在加電過程中,FPGA檢測到nCONFIG由低到高的跳變時,就開始準(zhǔn)備配置FPGA將CONF_DONE拉低,驅(qū)動EPC2的nCS為低,而nSTATUS引腳釋放并由上拉電阻拉至高電平使能EPC2此后,EPC2就用其內(nèi)部振蕩器的時鐘將數(shù)據(jù)串行地從EPC2DATA輸送到FPGADATA0當(dāng)配置完成后,FPGA釋放CONF_DONE,將EPC2與系統(tǒng)隔離

被動串行配置由編程硬件通過ByteBlaster配置ByteBlaster產(chǎn)生一個由低到高的跳變送到nCONFIG引腳,然后由編程硬件將配置數(shù)據(jù)送到DATA0引腳,該數(shù)據(jù)鎖存至CONF_DONE變?yōu)楦唠娖綖橹巩?dāng)CONF_DONE變成高電平時,用DCLK的10個周期初始化FPGA,器件的初始化由下載電纜自動執(zhí)行

為了兩種配置方式共存,設(shè)計中用撥碼開關(guān)將EPC2與FPGA和ByteBlaster的下載電纜插座隔離當(dāng)用被動串行方式配置時,撥碼開關(guān)斷開,由上位機通過ByteBlaster下載電纜加載FPGA當(dāng)用主動串行方式配置時,撥碼開關(guān)接通,由EPC2加載FPGA電路圖如圖2所示

評論