關(guān)于降低RFID應(yīng)答器功耗設(shè)計

當(dāng)RFID應(yīng)答器從系統(tǒng)的最小范圍運動到最大范圍時,其功率大致變化三十倍,所以RFID應(yīng)答器的功率要求可能對設(shè)計師提出了一個難于預(yù)測的挑戰(zhàn)。盡管UHFRFID應(yīng)答器可以獲得的典型功率在一百毫瓦數(shù)量級,但該問題并非僅限于功耗。即使是在短距離內(nèi),可以對應(yīng)答器提供足夠的功率卻可能導(dǎo)致電壓過載。應(yīng)答器還必須工作在從-25℃~+40℃的標(biāo)稱工作范圍內(nèi),以及從-40℃~+65℃基于EPCGen2標(biāo)準(zhǔn)的擴(kuò)展溫度范圍內(nèi)。

成本與功率要求極大地影響了對用于生產(chǎn)RFID應(yīng)答器IC的工藝選擇。正如在先前系列文章中所提到的,肖特基接觸在RFID應(yīng)答器設(shè)計中提供了低開啟電壓、低結(jié)電容以及高電流驅(qū)動。另外,已經(jīng)有人致力于采用新的工藝,例如BiCMOS以及藍(lán)寶石硅片(SOS),其提供了極佳的低功耗性能。但每種方法都有其不利的一面。在CMOS工藝中肖特基接觸并非是常規(guī)的,而一般需要后處理步驟。其它工藝諸如BiCMOS和SOS對大多數(shù)RFID應(yīng)答器應(yīng)用而言又太貴了。

實現(xiàn)低功耗電路要求的另一個方法是動態(tài)閾值電壓MOSFET(DTMOS)技術(shù)。其可以利用體硅CMOS技術(shù)實現(xiàn)廉價生產(chǎn)。其全部優(yōu)勢非常適合于開發(fā)下一代UHFRFID應(yīng)答器,本文將對此作詳細(xì)論述。本文將首先介紹DTMOS的基本原理。接下來,DTMOS在數(shù)字、模擬以及射頻領(lǐng)域的實現(xiàn)將被重點說明,這是由于UHFRFID應(yīng)答器包括了涉及所有這三個領(lǐng)域的電路。最后,將演示滿足EPCGen2指標(biāo)UHFRFID的DTMOS帶隙參考電路的芯片實現(xiàn)。

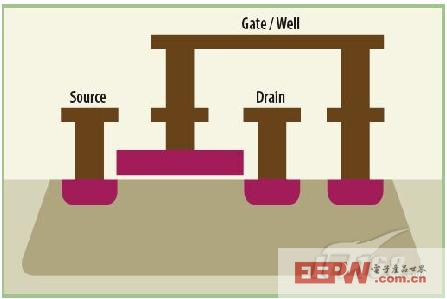

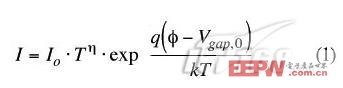

DTMOS屬于基本上采用互連的阱和柵的MOS晶體管(圖1)。對于雙阱p襯底CMOS工藝,由于只能單獨控制和生產(chǎn)N阱的這一事實,所以只能采用P型DTMOS,這是因為N型DTMOS的P阱具有到P襯底的共同和低歐姆的通路。然而,N型DTMOS可以在具有深N阱特性的工藝中獲得。DTMOS的操作類似于弱反型MOS的操作,相似于橫向PNP管中的三極管操作。弱反型MOS晶體管的漏電流與橫向PNP的集電極電流(都在飽和區(qū))為:

其中:F=FBJT=VBE。用于三極管,F(xiàn)=FWIM=[(VGS-VT)×COX/(COX+Cdepletion)]

用于弱反型MOS晶體管。

耗盡層電容的值依賴于耗盡層的寬度,其依次依賴于阱的摻雜特性,以及在硅中源極結(jié)附近的電壓降。因此,該因素依賴于所采用的阱-源電壓和通過閾值調(diào)制效應(yīng)所采用的阱-源電壓。

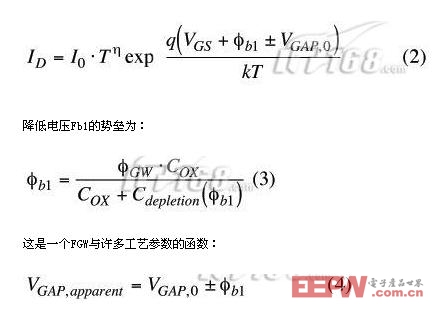

DTMOS可以被看作基極上具有額外柵的橫向雙極PNP管?;谶@一觀點,DTMOS的漏電流主要取決于通過源—阱結(jié)的電壓,其在VGS與ID之間產(chǎn)生了理想的指數(shù)(類似雙極)關(guān)系。由于互連柵—阱的存在,在柵和阱之間存在著內(nèi)建電壓FGW。由于電容的分配,電壓FGW在柵氧和硅上被再次分配。這意味著硅中的電壓降由于FGW作為勢壘,降低了電壓Fb1,DTMOS的漏電流可以表示為:

由這些推導(dǎo)得出的關(guān)鍵結(jié)果如下:

1.與硅PN結(jié)的1.2V相比,DTMOS器件的帶隙顯然是0.6V;

2.DTMOS器件具有理想的指數(shù)特性[IDaexp(qVGS/kT)];

3.DTMOS器件的橫向電流具有exp(qFb1/kT)因子,其比通常的橫向PNP要大;

4.帶隙電壓具有明顯的溫度依賴性。采用0.25umDTMOS工藝生產(chǎn)的初步成功設(shè)計工作在77K溫度下,使用0.6V電源電壓并將襯底連接到固定的正向偏置電壓。接下來的試驗包括受控柵橫向雙極晶體管(GCLPNP)以及襯底連接到柵端的硅絕緣體(SOI)MOSFET工藝。第一種工藝用于小型的低功耗模擬應(yīng)用,而第二種工藝是超低功耗CMOS的典型最佳候選技術(shù)。

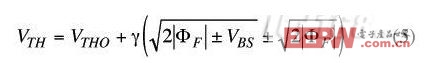

DTMOS技術(shù)在其產(chǎn)生的柵—延遲/功耗方面與傳統(tǒng)的CMOS技術(shù)相比顯示出驚人的性能優(yōu)勢。DTMOS還在RF電路中顯示出優(yōu)越性能。在傳統(tǒng)的CMOS中,縮小到更小特征尺寸和閾值電壓(VTH)的工藝增加了工作速度。然而,VTH的降低也導(dǎo)致了亞閾值MOSFET行為的下降。靜態(tài)電路中靜態(tài)電流的增加,將VTH限制為0.4V。DTMOS可能可以克服這些約束,特別是工作在具有陡峭的亞閾值特性的極低VDD和低VTH下。對DTMOS,柵輸入電壓正向偏置了襯底,根據(jù)著名的體效應(yīng)公式,VTH將降低:

評論