TMS320C54xx與TLV320AIC24型編解碼器接口

1 前言

TMS320C54xx是TI公司生產(chǎn)的具有較高性價(jià)比的DSP系列,采用高性能的改進(jìn)型哈佛總線結(jié)構(gòu);內(nèi)含一個(gè)40bit的算術(shù)邏輯單元(包括一個(gè)40bit的筒形移位器和兩個(gè)獨(dú)立的加法器)、軟件可編程等待狀態(tài)發(fā)生器以及可編程分區(qū)轉(zhuǎn)換邏輯電路;同時(shí)帶有內(nèi)部振蕩器或用外部時(shí)鐘源的片內(nèi)鎖相環(huán)(PLL)時(shí)鐘發(fā)生器;該DSP帶有全雙工串行口,支持8位或16位傳送;同時(shí)帶有時(shí)分多路串行口、緩沖串行口、16位可編程定時(shí)器、8位并行主機(jī)接口等;可用外部總線進(jìn)行關(guān)斷控制,以斷開外部數(shù)據(jù)總線、地址總線和控制信號(hào);數(shù)據(jù)總線具有總線保持特性。

TI公司的TLV320AIC24型多媒體數(shù)字信號(hào)編解碼器則可提供時(shí)分復(fù)用串行口(SMARTDM),并可用一個(gè)先進(jìn)的TDM格式同步4線串行口以優(yōu)化DSP的性能,從而實(shí)與流行DSP(如C5000、C6000)和微控制器的無縫連接。SMARTTDM提供了連續(xù)數(shù)據(jù)轉(zhuǎn)換和再配置編程兩種模式(ADC/DAC和控制數(shù)據(jù)),可使TLV320AIC24 DSP編碼器和DSP數(shù)據(jù)轉(zhuǎn)換的帶寬最大化(只對(duì)ADC/DAC數(shù)據(jù))。在一般的操作中,它會(huì)自動(dòng)發(fā)現(xiàn)串行接口中的編碼個(gè)數(shù)并調(diào)整時(shí)鐘數(shù)以與編碼數(shù)據(jù)相匹配。而在TURBO操作中,它可以保持相同的時(shí)鐘數(shù)值,但位轉(zhuǎn)換率最大到達(dá)25MHz,允許其他的DSP外圍串行器件在相同的采樣周期內(nèi)分離相同的串行總線。TLV320AIC24支持任意基于SMARTDM的器件級(jí)聯(lián),實(shí)現(xiàn)多通道編碼(最多可有8路TLV320AIC24編碼級(jí)聯(lián)到單個(gè)串行口),它所支持的3種串行口配置為單機(jī)主、單機(jī)從和級(jí)聯(lián)主從模式。

TLV320AIC24還提供兩種16位Σ-△A/D通道和16位Σ-△D/A通道,可連接到手機(jī)、耳機(jī)、麥克風(fēng)等外部設(shè)備;其嵌入的模擬和數(shù)字側(cè)音、反偏濾波器、可編程輸入輸出增益控制等電路楞為麥克風(fēng)提供前置放大和150Ω負(fù)載、硬件/軟件控制的掉電模式等功能;TLV320AIC24具有和TMS320C54xx完全兼容的電源電壓;其可編程最高采樣率達(dá)26ks/s(用片上IIR/FIR濾波器)和104ks/s(用IRR/FIR側(cè)通);在8ks/s的采樣率下,它們的片上FIR可產(chǎn)生87dB的動(dòng)態(tài)范圍(對(duì)ADC)和92dB的動(dòng)態(tài)范圍(對(duì)DAC);ADC和DAC濾波器符合G.711和G.722協(xié)議。此外,TLV320AIC24還提供了一個(gè)靈活的主機(jī)接口(一個(gè)可以編程為標(biāo)準(zhǔn)工業(yè)I2C總線協(xié)議或S2C總線協(xié)議的2位串行口)。

2 硬件接口

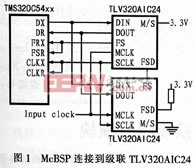

DSP McBSP和TLV320AIC24的接口方式為4路SMARTDM信號(hào),分別為幀同步、串行數(shù)據(jù)輸出、串行數(shù)據(jù)輸入和時(shí)鐘源,它們分別連接到FSX/FSR、DR、DX、CLKX/CLKR。在級(jí)聯(lián)模式下,DSP可通過主器件的FS端接收幀同步信號(hào),主器件的FDS端連接到第一級(jí)從器件的FS端,而將第一級(jí)從器件的FSD連接到第二級(jí)從器件的FS端,如此類推。最后一級(jí)的FSD通過電阻器連接到3.3V電源輸入端。圖1給出級(jí)聯(lián)TLV320AIC24和DSP的連接方式。

3 軟件編程

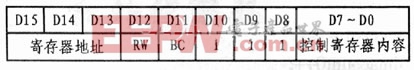

TLV320AIC24的每一個(gè)通道都含有6個(gè)控制寄存器,可以編程所需的操作模式。在控制幀模式下,通過DIN引腳可以對(duì)所有的寄存器進(jìn)行編程。在一個(gè)幀同步延時(shí)后,新的配置生效。上電后,TLV320AIC24被默認(rèn)為編程模式。設(shè)置控制寄存器1到第6位可用于轉(zhuǎn)換連續(xù)數(shù)據(jù)模式。如果采用15+1數(shù)據(jù)格式,那么,把DIN的最低位設(shè)置成1可將連續(xù)數(shù)據(jù)傳輸模式轉(zhuǎn)換成編程設(shè)置模式。其格式如下:

其中,D15-D13位為控制寄存器地址,操作時(shí)可與位D7-D0所攜帶的數(shù)據(jù)一塊寫入;位D12用于確定對(duì)所尋址寄存器的讀寫;位D11用來確定是否選擇廣播模式;位D10-D8永遠(yuǎn)設(shè)置為1。

下面給出編碼器寄存器的編程例子。其中,DSP通過DMA連接到SMARTDM以對(duì)TLV320AIC24進(jìn)行初始化。DMA是指在不需要CPU干預(yù)的情況下,在映射存儲(chǔ)區(qū)的不同區(qū)間傳輸數(shù)據(jù)的技術(shù)。DMA可支持上存儲(chǔ)器、片上外設(shè)(包括EHPI8)或是外部設(shè)備間無CPU負(fù)責(zé)的獨(dú)立數(shù)據(jù)交換。

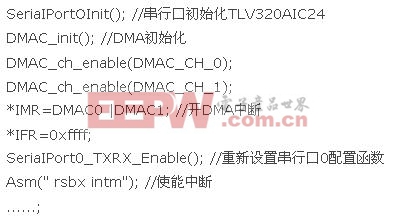

(1)初始化

?。?)DMA0中斷服務(wù)子程序,進(jìn)行數(shù)據(jù)接收

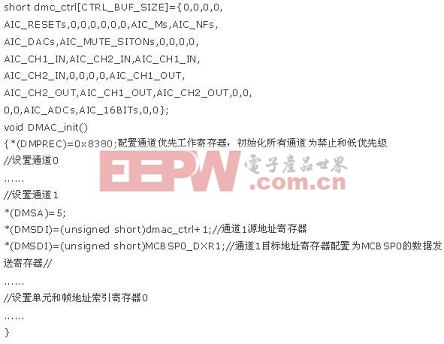

?。?)用DMA初始化TLV320AIC24子程序

4 結(jié)束語

本文介紹的硬件設(shè)計(jì)方法和軟件編程可以完成語音信號(hào)的采集與回放,從而實(shí)現(xiàn)語音數(shù)據(jù)的采集、處理和存儲(chǔ)等功能。該方案能夠滿足主流語音處理產(chǎn)品的要求,可以廣泛應(yīng)用在各種相關(guān)設(shè)備中。

評(píng)論