vhdl-ams 文章 進入vhdl-ams技術社區(qū)

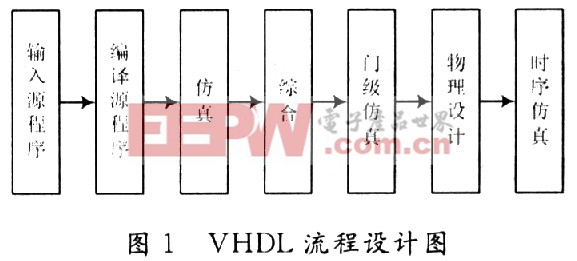

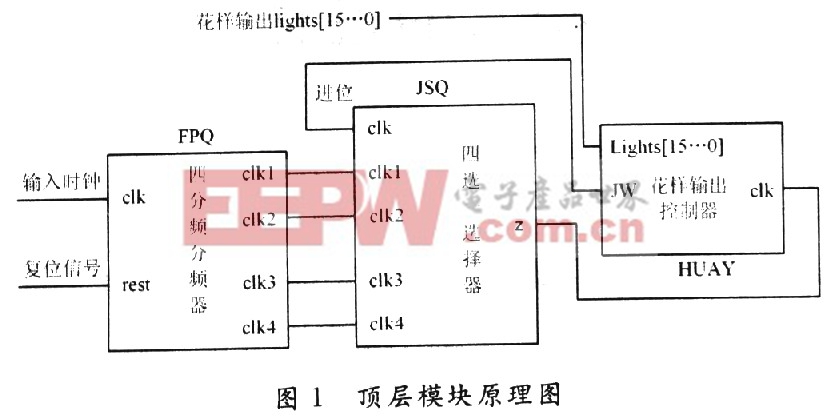

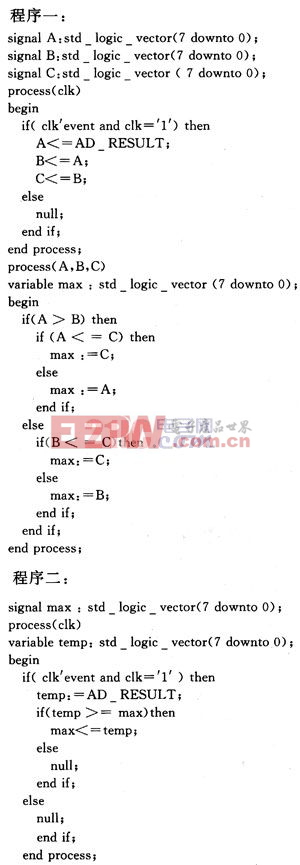

基于CPLD/FPGA的VHDL語言電路優(yōu)化設計

- VHDL(VeryHighSpeedIntegratedCircuitHardwareDescriptionLanguage)是IEEE工業(yè)標準硬件描述語言...

- 關鍵字: CPLD FPGA VHDL 電路優(yōu)化設計

vhdl-ams介紹

即IEEE 1076.1標準。

VHDL-AMS是VHDL的一個分支,它支持模擬、數(shù)字、數(shù)?;旌想娐废到y(tǒng)的建模與仿真。

http://www.eda.org/vhdl-ams/

Verilog-AMS與之類似。支持模擬、數(shù)字、數(shù)?;旌想娐废到y(tǒng)的建模與仿真。

http://www.eda.org/verilog-ams/

The VHDL-AMS language [ 查看詳細 ]

關于我們 -

廣告服務 -

企業(yè)會員服務 -

網站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司